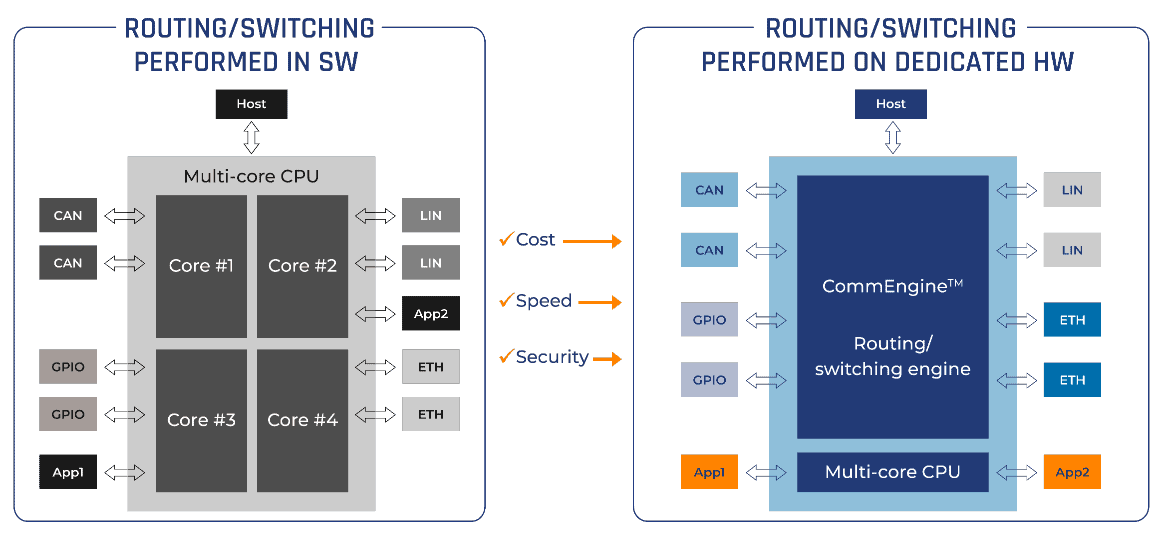

Latency reduction for routing/switching by a factor of up to 10x through massive parallelization. Even functionality with deterministic low latency requirements can now be confidently routed via zonal gateways with guaranteed throughput.

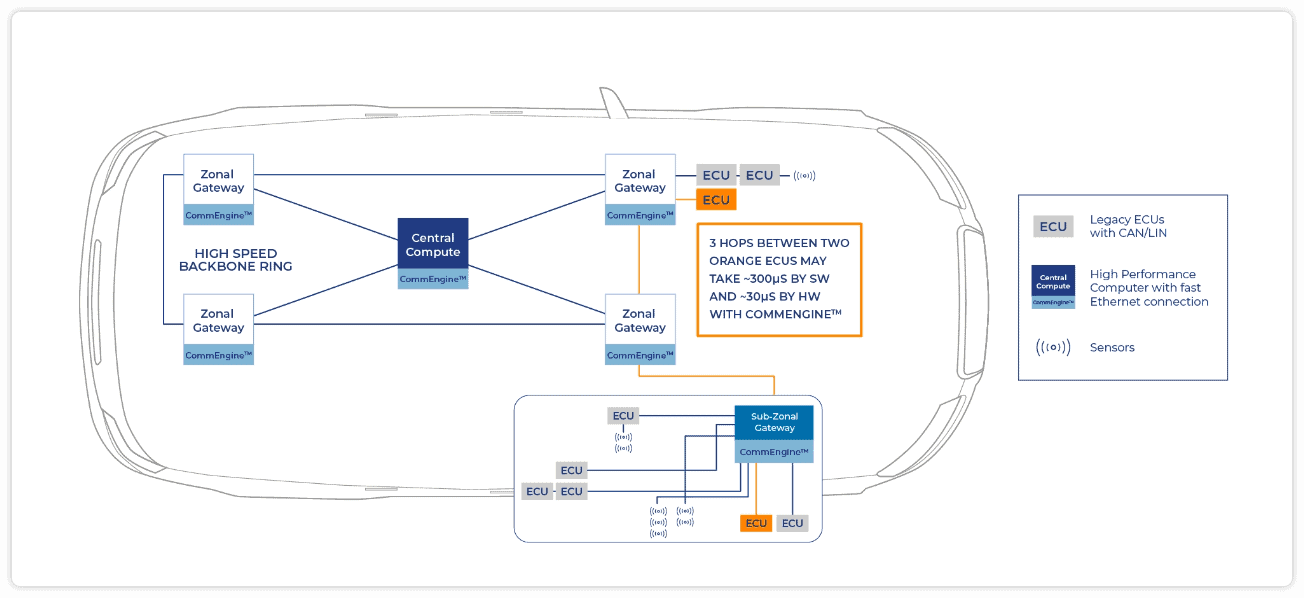

Automotive E/E topologies are moving toward architectures where domain-centered and zone-centered configurations are used to consolidate the functionality of multiple ECUs and enable size and weight reduction of the wiring harness. In zonal routers, a combination of microcontroller and Ethernet switches can be used, however, such a design quickly leads to timing and routing problems. This is because Zonal Architecture requires signals or messages to pass through several hops (as each ECU takes a small amount of time from when a message arrives to when it leaves), whose latencies then add up. The cumulative latency can quickly exceed the limits set by the system, especially due to unpredictable fluctuations in states of high load.

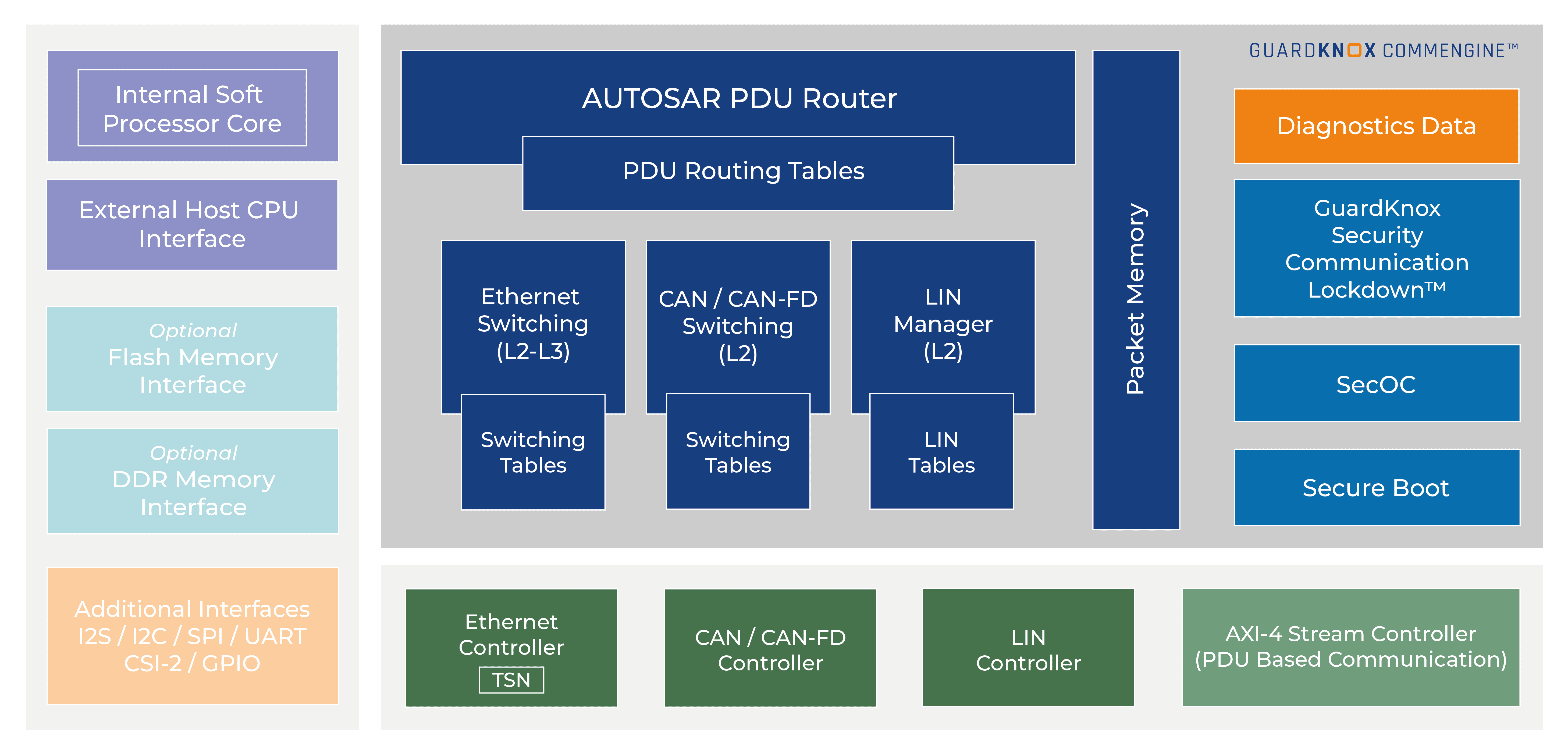

GuardKnox’s CommEngineTM is a single-chip solution that implements Zonal Gateway functionality and enables high-performance and cost-effective data routing. It is available as a highly integrated IP Core, running on an FPGA or ASIC. The secure-by-design routing-technology implemented in hardware allows deterministic ultra-low latency with multi-gigabit bandwidth. The product enables next generation automotive E/E architectures.

Latency reduction for routing/switching by a factor of up to 10x through massive parallelization. Even functionality with deterministic low latency requirements can now be confidently routed via zonal gateways with guaranteed throughput.

Integration into one chip or IP core reduces the number of required IC’s and therefore reduces the cost significantly without limiting scalability and functionality. No time-consuming and complex vehicle network optimizations are required for deployment.

Increased flexibility (e.g., ports, protocols) in early stages through FPGA implementation with no need for long and complex redevelopments (e.g., switch to another MCU/MPU platform). Additionally routing tables can be easily updated via ARXML upload.

Completely synthesizable to any ASIC or FPGA technology per vehicle requirements.

GuardKnox’s CommEngineTM enables the move to next generation centralized E/E architectures by guaranteeing a high throughput with a very low latency. It also provides deterministic switching/routing performance with high functional flexibility while staying cost-aware.

It creates a latency reduction for routing/ switching by a factor of up to 10x through parallelization. Even functionality with low latency requirements can now be routed via Zonal Gateways with guaranteed throughput up to 10Gbit/s eliminating the time-consuming and complex vehicle network optimizations necessary in legacy architectures.

The integration of switching/routing into a single chip creates significant direct cost benefits (packaging, size) without limiting scalability or functionality.

The CommEngineTM Increases flexibility (e.g., ports, multi-protocol support) in early stages through its FPGA implementation without the need for lengthy and complex re-developments (Such as switching to another MCU/MPU platform). It updates routing tables easily via ARXML upload.

Once requirements mature, there is a straightforward transition to ASIC, reducing chip costs for long-term production.

GuardKnox’s CommEngineTM:

In microcontroller-based routers, the broad compatibility provided by the use of AUTOSAR software stacks is bought with, depending on the processor load, strongly fluctuating routing latency times of typically 100 μSec up to a few msec. In an FPGA, on the other hand, data flows through an application-specific pipeline and even complex operations, such as resolving the CAN ID to find the routing destination of an incoming message require only a few clock cycles. Parallel processing pipelines are implemented for each interface and operate independently of each other, so that routing latency times of a few μSec per hop are deterministically achievable without extensive optimization. The high performance allows additional security measures through real-time filters, such as Communication Lockdown from GuardKnox.

To implement this function, filters integrated in the FPGA can check all data packets in real time against the CAN database to determine whether signal values are valid. In addition, FPGA filters can monitor the repetition rates of certain cyclic messages, which are also specified in the CAN database, in order to detect sensor errors or possible denial-of-service (DOS) attacks. In both cases, unnecessary data traffic and processing load can be avoided by not forwarding repeated messages and optionally generating programmable status messages.

The CommEngineTM offers multiple implementation options with interfaces and cores added or removed per need:

CommEngineTM integrated in HPC (High Performance Compute) for interconnection of high-bandwidth communication backbone and external sensors, ECUs, and Gateways.

Targeted at Zonal Gateway application and used for routing between low-speed and high-speed interfaces, PDU construction and reconstruction, streaming, security, and multi-gigabit switching. Additional computation cores MCU/CPU/GPU/NPU can be added or removed according to specific applications acceleration needs.

Targeted at localized aggregation of low bandwidth interfaces (CAN, LIN, sensors, I/O) into a single high-bandwidth upstream interface (Ethernet) such as a sub-zonal door module.